1. Introduction

Crystal Oscillators generate highly stable clock signals that are needed in almost all electronic systems – from simple microcontroller circuits to high-speed data transmission systems.

The output signal of an oscillator must be compatible with the downstream logic family or interface. Over the decades, various output standards have evolved, each tailored to the requirements of their era and application.

This document provides a comprehensive overview of the seven most common output signal types in crystal oscillators: CMOS, TTL, Clipped Sine Wave, Sine, LVPECL, LVDS and HCSL.

For each type, the historical development, electrical characteristics, typical waveform, and preferred applications are explained.

2. Historical Development

The development of output signal types can be closely linked to the evolution of semiconductor technology and increasing demands on clock frequencies and signal integrity:

2.1 TTL (Transistor-Transistor Logic) – from approx. 1964

TTL was one of the first widely used digital logic standards and was introduced by Texas Instruments as the 7400 series. Oscillators with TTL output operate at a supply voltage of 5 V and deliver level ranges that are directly compatible with TTL gates. The standard shaped digital electronics for decades and was the dominant logic standard until the 1990s.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – from approx. 1968

CMOS technology was originally developed by RCA and is characterized by extremely low quiescent current consumption. CMOS oscillators provide rail-to-rail output signals, meaning the output oscillates almost entirely between 0V and VCC. With ongoing miniaturization and the trend towards lower supply voltages (3.3V, 2.5V, 1.8V), CMOS has become the most widely used output standard for crystal oscillators.

2.3 Sine – Since the Beginnings of Oscillator Technology

Sinusoidal output signals are as old as oscillator technology itself. Crystal oscillators physically oscillate sinusoidally; all other signal shapes are generated by downstream circuitry. Sine wave outputs are preferred in high-frequency technology, measuring instruments, and analog signal processing because they do not generate harmonics.

2.4 Clipped Sine Wave – from approx. 1970s

The clipped sine wave output represents a compromise between sine and square wave output. The sine signal is limited (clipped) at the peaks, creating steeper edges than pure sine but fewer harmonics than a square wave signal. This output type was particularly used in telecommunications and older high-frequency applications. Clipped sine wave ICs are still mainly used in TCXOs today. This technology allows significantly more power-efficient TCXOs to be built than with CMOS technology. CSW-TCXOs are therefore used as references in navigation devices, emergency call systems, and gateways. Wherever signal range (radio) and highly accurate positioning are required.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – from approx. 1990s

With the demand for ever-higher clock frequencies in network and telecommunications systems, LVPECL emerged as a fast differential output logic. LVPECL is based on classic ECL technology (Emitter-Coupled Logic), which was developed in the 1960s for high-speed applications, and adapts it for lower supply voltages (3.3 V instead of -5.2 V). LVPECL offers extremely short switching times and is suitable for frequencies well above 1 GHz.

2.6 LVDS (Low-Voltage Differential Signaling) – from 1994

LVDS was introduced in 1994 as the ANSI/TIA/EIA-644 standard and optimizes differential signal transmission for low power consumption and high data rates. The small differential voltage swing of only 350 mV enables fast switching with minimal electromagnetic radiation. LVDS is now widely used in display interfaces, serial data links, and FPGA clocking.

2.7 HCSL (High-Speed Current Steering Logic) – from approx. 2002

HCSL was specifically developed for the PCI Express standard and has been the reference clock standard since the first PCIe generation. The PCI-SIG specified HCSL as a current-mode-based differential signal with very low voltage swing, optimized for 100 MHz reference clocks in PCIe systems. HCSL is now indispensable in every PC, server, and embedded system with a PCIe interface.

3. Aperçu des formes de signaux

Les diagrammes suivants montrent les formes de signaux idéalisées des sept types de sortie. Notez les différentes plages de tension et excursions – celles-ci sont déterminantes pour la compatibilité avec les récepteurs en aval.

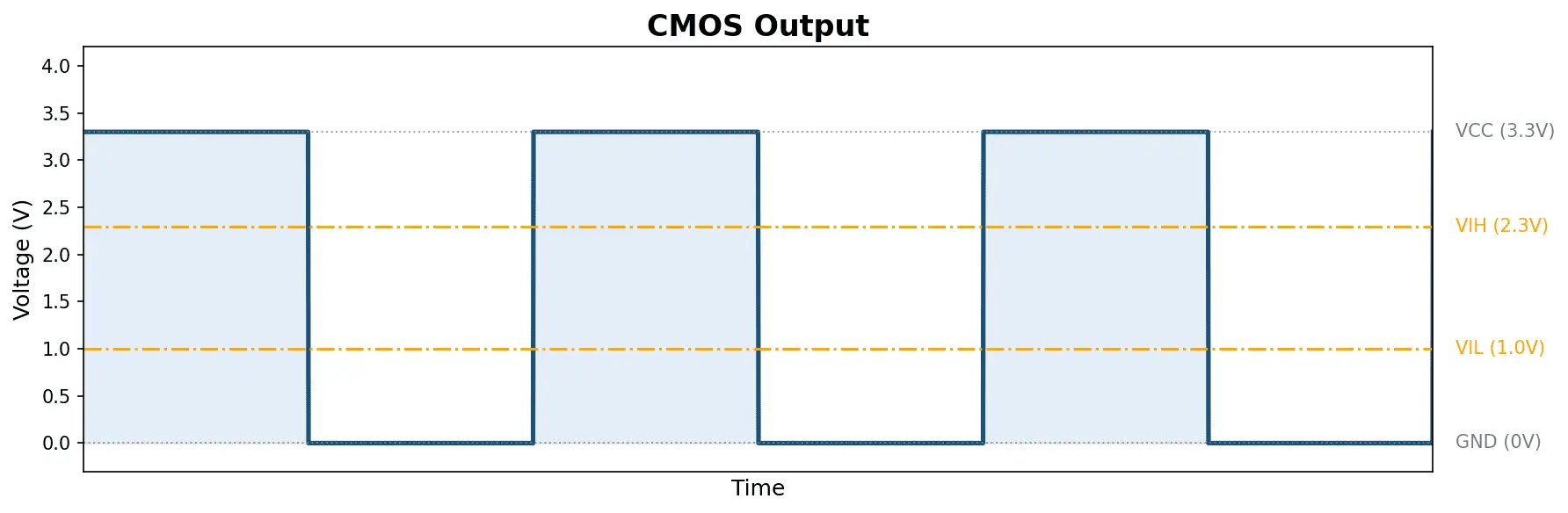

3.1 CMOS

Fig. 1: CMOS output signal – Rail-to-rail square wave between 0 V and VCC (here 3.3 V)

The CMOS signal is characterised by its full voltage swing between GND and VCC. The input thresholds VIL and VIH are typically 30 % and 70 % of VCC respectively, which ensures a wide signal-to-noise ratio. The symmetrical output driver structures (P-channel/N-channel MOSFET) enable almost identical rise and fall times.

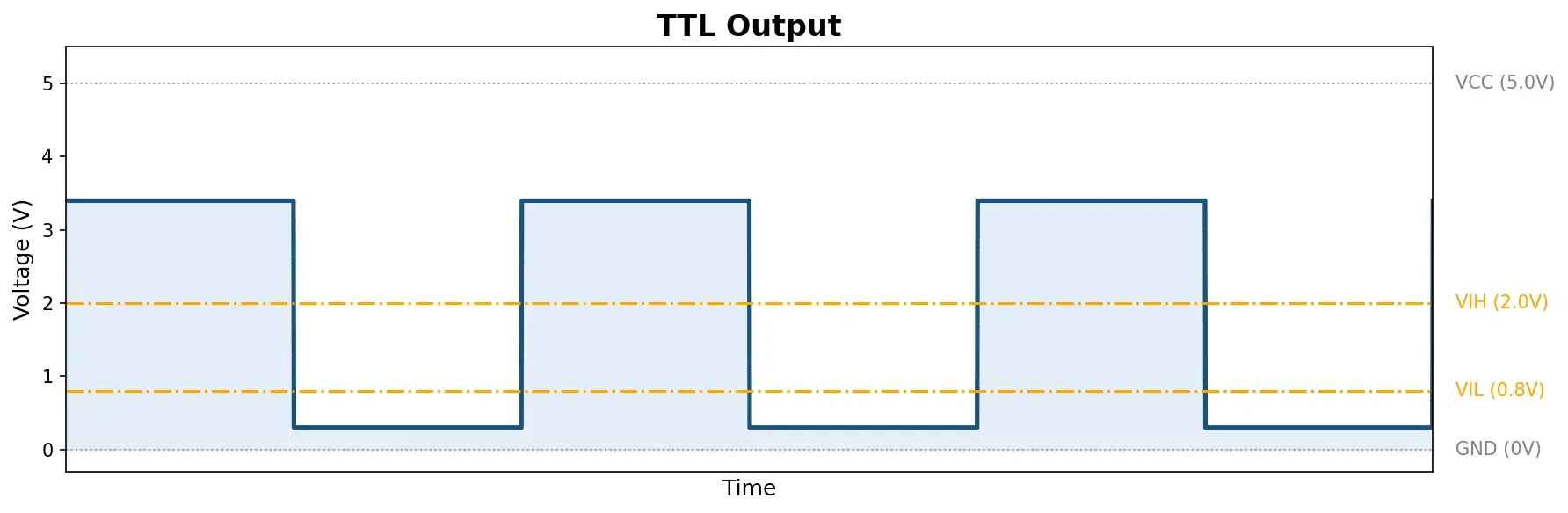

3.2 TTL

Fig. 2: TTL output signal – VOH typically 3.4 V, VOL typically 0.3 V at 5 V supply

Unlike CMOS outputs, TTL transistors do not achieve rail-to-rail levels. The high level (VOH) is typically 3.4V (minimum 2.4V), and the low level (VOL) is a maximum of 0.4V. The asymmetrical thresholds (VIL = 0.8V, VIH = 2.0V) result from the bipolar transistor architecture. The so-called "forbidden range" between 0.8V and 2.0V must not be assumed during static operation.

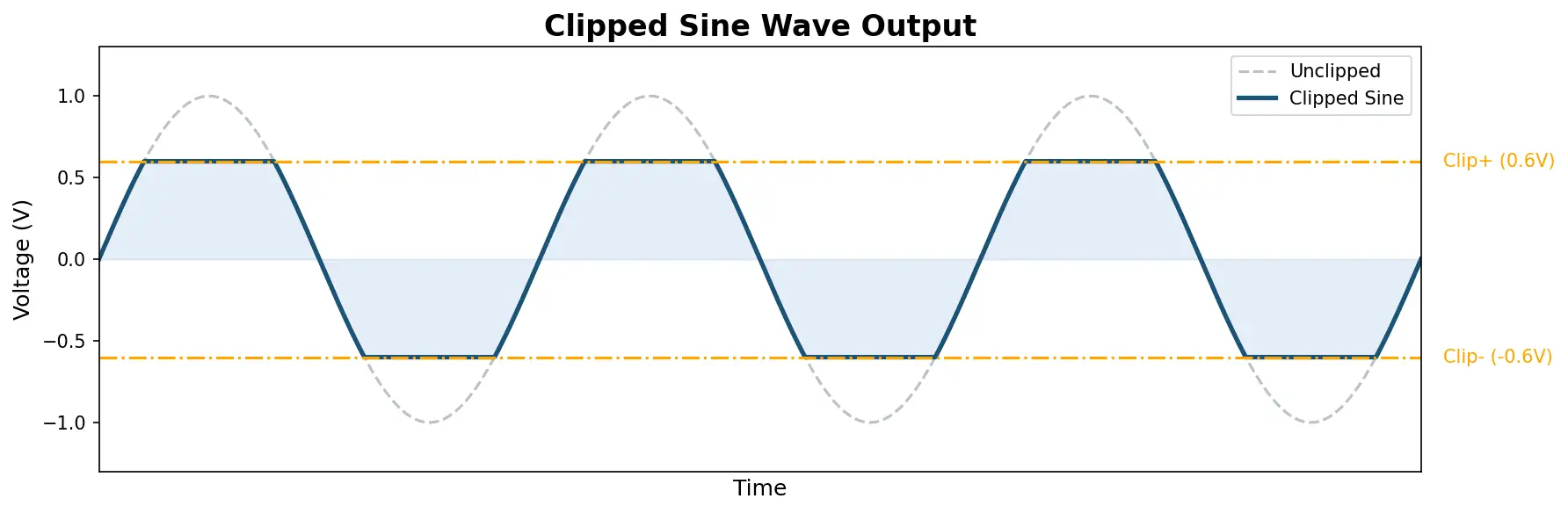

3.3 Clipped Sine Wave

Fig. 3: Clipped sine wave output – Sine signal with limited amplitude peaks

With the clipped sine wave output, the natural sine signal of the crystal resonator is limited at defined threshold values. The dashed line shows the unclipped sine waveform. The clipping creates steeper zero crossings than with pure sine, facilitating driving downstream logic, while the harmonic content remains moderate.

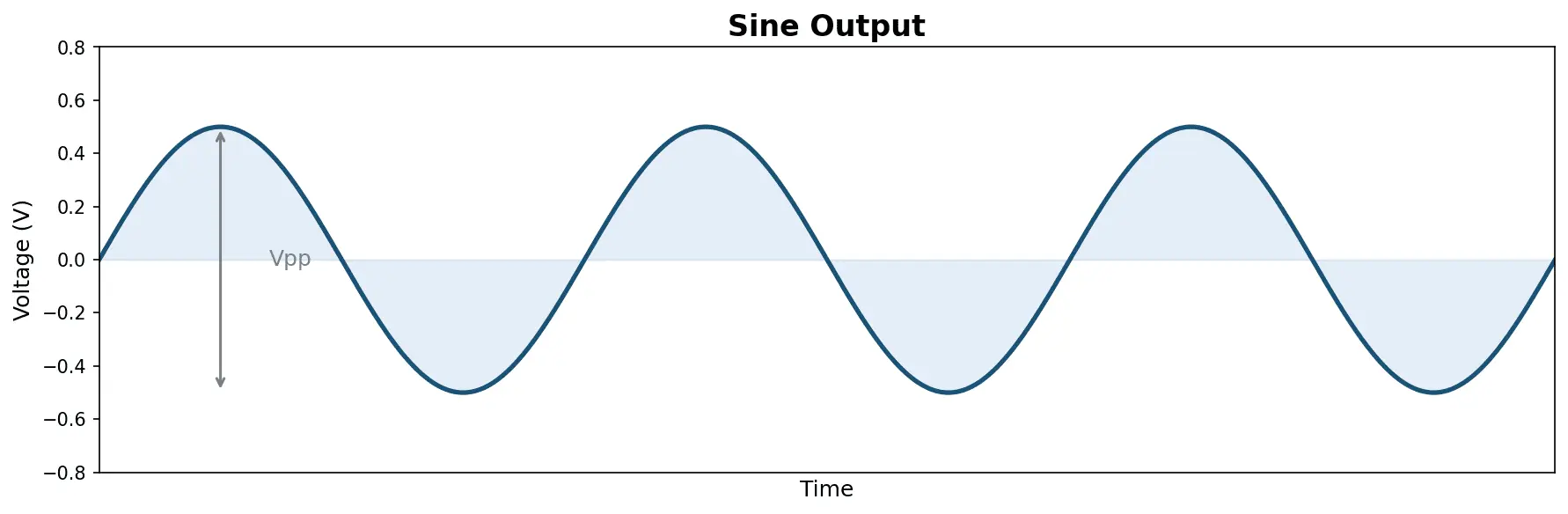

3.4 Sine

Fig. 4: Sine output – Pure sine signal with defined peak-to-peak voltage (Vpp)

The sine output delivers the cleanest spectrum of all output waveforms: ideally only a single spectral line at the fundamental frequency. The amplitude is specified as peak-to-peak voltage (Vpp) or as power in dBm. Typical values are 0.5 to 1.0 Vpp or 0 to +13 dBm in 50 Ω systems.

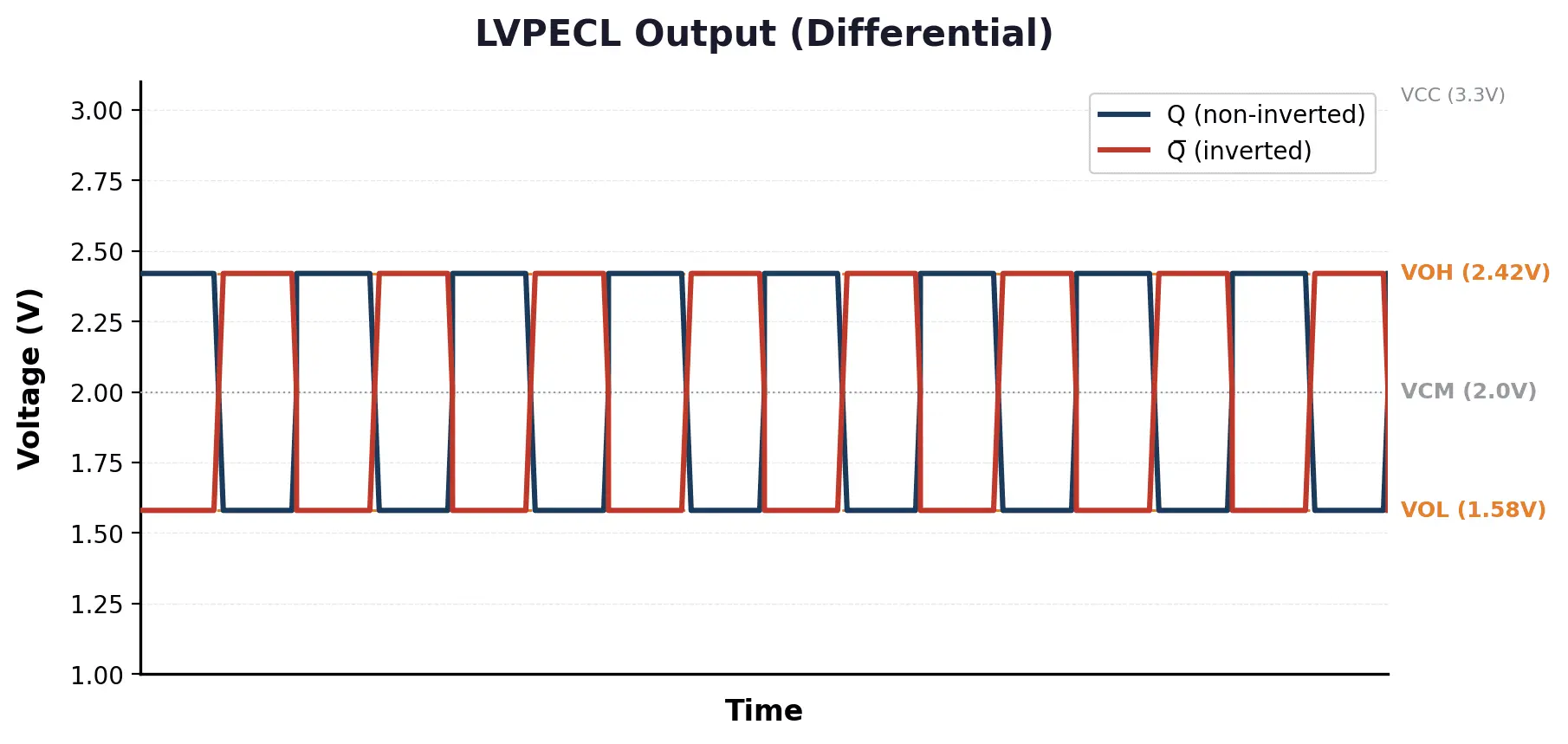

3.5 LVPECL

Fig. 5: LVPECL output – Differential signal with approx. 800 mV total swing around VCC–1.3 V

LVPECL uses differential signal routing: Two complementary outputs (Q and Q̅) swing in anti-phase around a common common-mode level (VCM), typically at VCC–1.3 V. The differential voltage swing is approx. 800 mV. The current source architecture enables extremely fast switching times with minimal overshoot tendency.

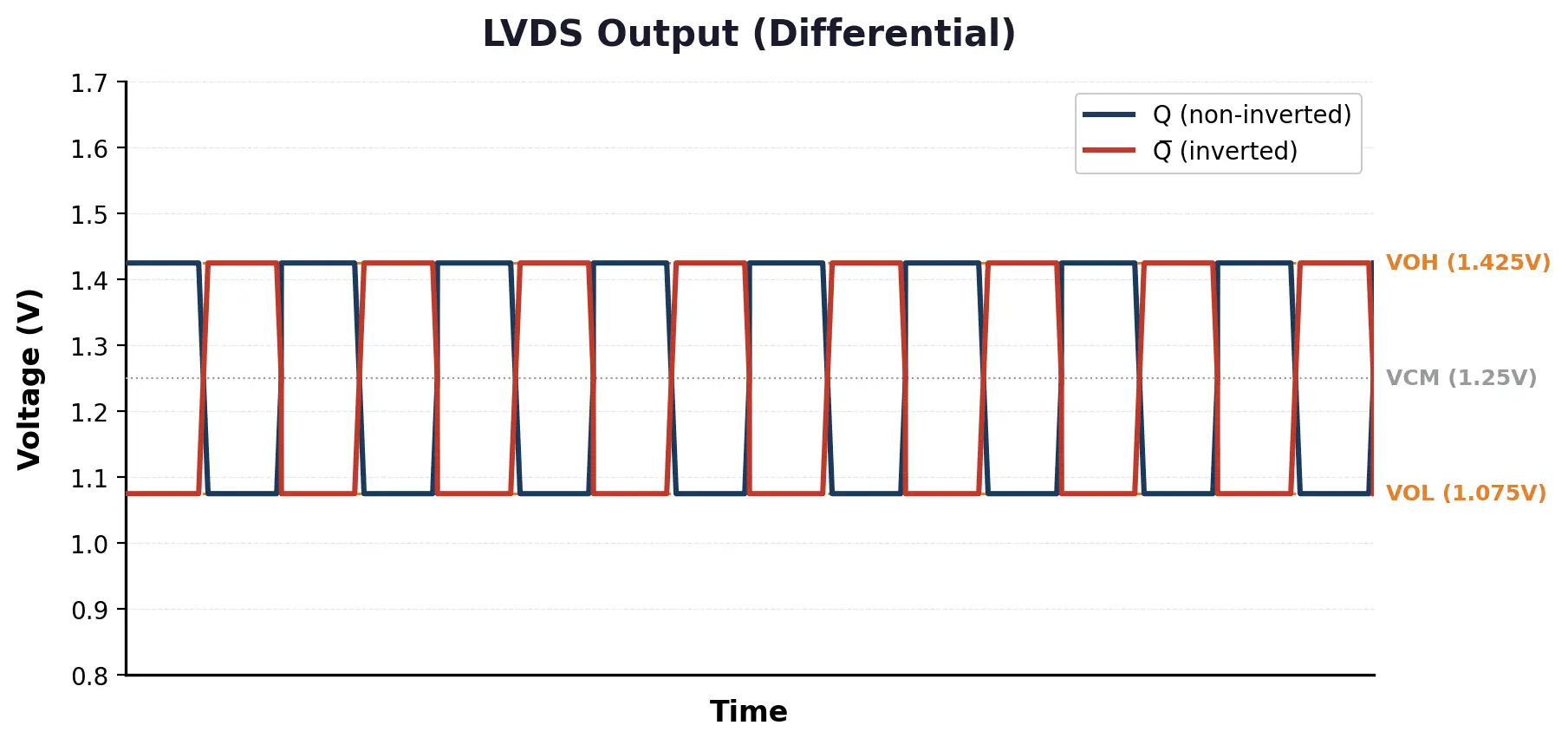

3.6 LVDS

Fig. 6: LVDS output – Differential signal with only 350 mV swing around 1.25 V common-mode level

LVDS is characterized by its particularly low differential voltage swing of only 350 mV. The common-mode level is at 1.25 V. Through the current-driven driver (typically 3.5 mA) and the 100 Ω termination, high signal integrity is achieved with minimal power consumption. The low amplitude minimizes electromagnetic radiation.

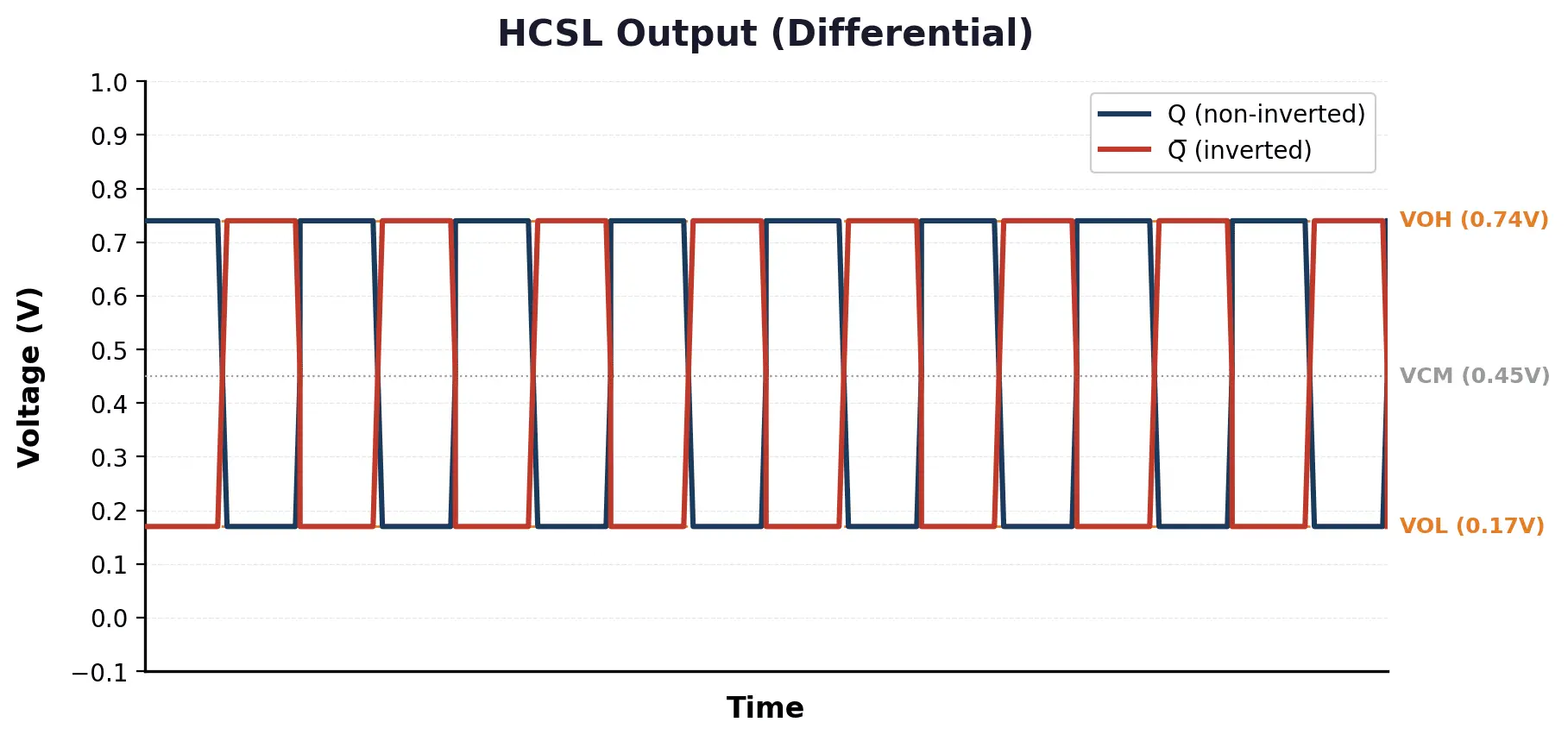

3.7 HCSL

Fig. 7: HCSL output – Current-mode-based differential signal for PCIe reference clocks

HCSL operates with a very low voltage swing: VOH is typically 0.74 V and VOL 0.17 V, resulting in a common-mode level of approx. 0.45 V. The current steering architecture is specifically optimized for the PCIe specification requirements and allows precise impedance matching via 50 Ω terminations to ground.

4. Comparison of Output Signals

The following table summarizes the key properties of all seven output types:

Type | Signal type | VCC (V) | VOH/ VOL (V) | Diff. Stroke | Max. approx. freq. | Typical application |

| CMOS | Single-ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Microcontrollers, FPGAs, general digital technology |

| TTL | Single-ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Legacy systems, industrial controls |

| Clipped Sine | Single-ended | 1,8/2,5/3,3 | variable | - | ~200 MHz | Telecommunications, RF applications |

| Sine wave | Single-ended | 3,3/5,0/12 | variable | - | >1 GHz | RF technology, measuring instruments, frequency synthesis |

| LVPECL | Differential | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Network equipment, SONET/SDH, high-speed clocking |

| LVDS | Differential | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Display interfaces, serial links, FPGA clocking |

| HCSL | Differential | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | PCI Express reference clock (100 MHz) |

5. Key Differences in Detail

5.1 Single-Ended vs. Differential

The most fundamental difference between output types is the signal routing. CMOS, TTL, Clipped Sine Wave, and Sine are single-ended signals – they reference to a common ground. LVPECL, LVDS, and HCSL, on the other hand, are differential signals with two complementary lines. Differential signals offer decisive advantages at higher frequencies: they suppress common-mode interference, enable smaller voltage swings, and thereby allow faster switching times with less electromagnetic radiation.

5.2 Voltage Swing and Noise Margin

CMOS offers the largest absolute voltage swing with its rail-to-rail output and thus the best static noise margin. TTL has a more limited noise margin due to its asymmetric levels. The differential standards (LVPECL, LVDS, HCSL) compensate for their smaller voltage swings through the common-mode rejection of differential transmission, making them often more reliable in noisy environments than single-ended signals.

5.3 Power Consumption

CMOS oscillators consume virtually no current in the static state; consumption increases proportionally with frequency (dynamic power dissipation). TTL has a constantly higher quiescent current consumption due to its bipolar architecture. LVPECL requires external termination resistors and has the highest power consumption of the differential standards. LVDS is known for its low power consumption (typically 3.5 mA driver current). HCSL falls between LVDS and LVPECL in terms of power consumption.

5.4 Frequency Range and Application Focus

For frequencies up to approximately 200 MHz, CMOS oscillators are the first choice in most cases due to their versatility, simple circuit design, and widespread availability. Above approximately 200 MHz, differential outputs are recommended. LVPECL offers the highest frequencies (>3 GHz) and is used in networking and telecommunications equipment. LVDS covers a broad mid-range and is particularly common in FPGA and display applications. HCSL is optimized for its niche use case: the 100 MHz reference clock for PCI Express.

5.5 Termination and Circuit Complexity

CMOS and TTL outputs generally require no external termination for short trace lengths – this makes them particularly easy to use. LVPECL mandatorily requires external termination resistors (typically: Thevenin termination to VCC–2 V or resistors to ground), increasing circuit complexity. LVDS is terminated by default with a 100 Ω differential resistor at the receiver. HCSL uses 50 Ω resistors to ground at each output.

6. Overshoot in Oscillator Output Signals

6.1 What is Overshoot?

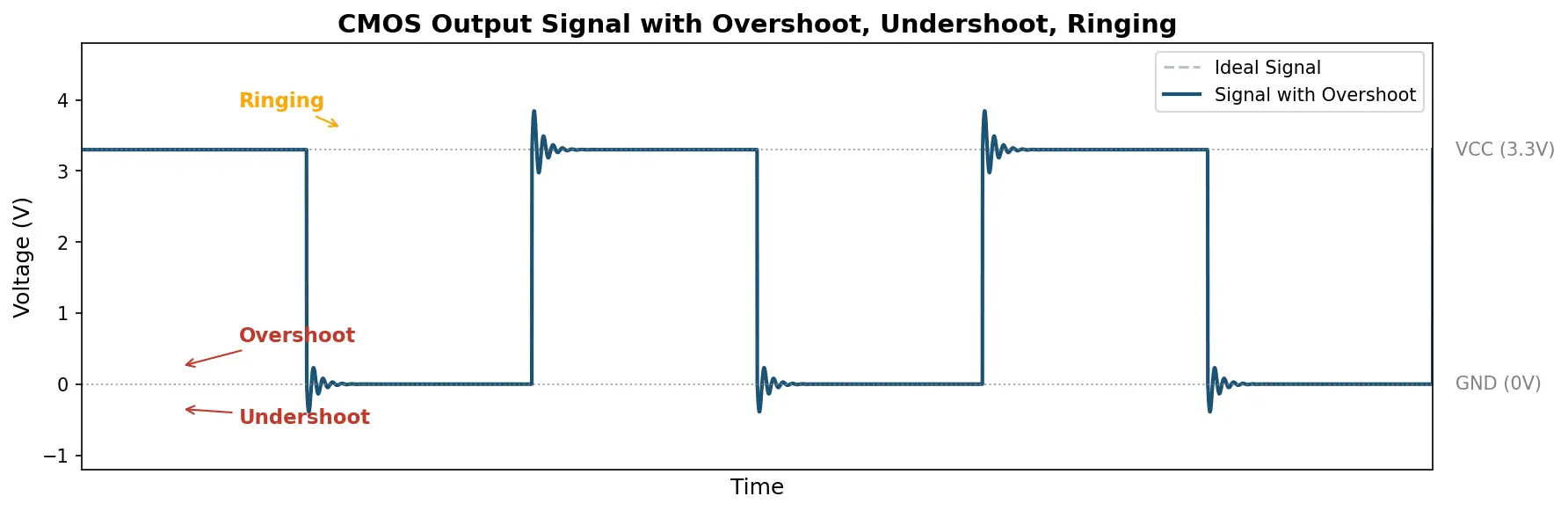

Overshoot and undershoot are brief voltage spikes that occur during rapid switching operations. On a rising edge, the voltage briefly exceeds VCC (overshoot), while on a falling edge, it drops slightly below GND (undershoot). These spikes are often followed by damped oscillations known as “ringing.”

The cause lies in the combination of very steep switching edges of the output driver and the parasitic inductances and capacitances of the trace, package, and load capacitance. Physically, a resonant circuit is formed from the trace inductance and the input capacitance of the receiver. The steeper the switching edge and the longer the trace, the more pronounced the overshoot.

Fig. 8: CMOS output signal with overshoot – Overshoot above VCC, undershoot below GND, and subsequent ringing

6.2 Why is Overshoot Problematic?

Overshoot exceeding VCC or dropping below GND can forward-bias the ESD protection diodes of the receiver IC, generating parasitic currents. In the worst case, this can lead to latch-up – an uncontrolled current flow through parasitic thyristor structures in the CMOS IC that can destroy the component. Severe ringing can also cause multiple triggering at clock inputs when the voltage crosses the switching threshold multiple times, leading to erroneous system behavior.

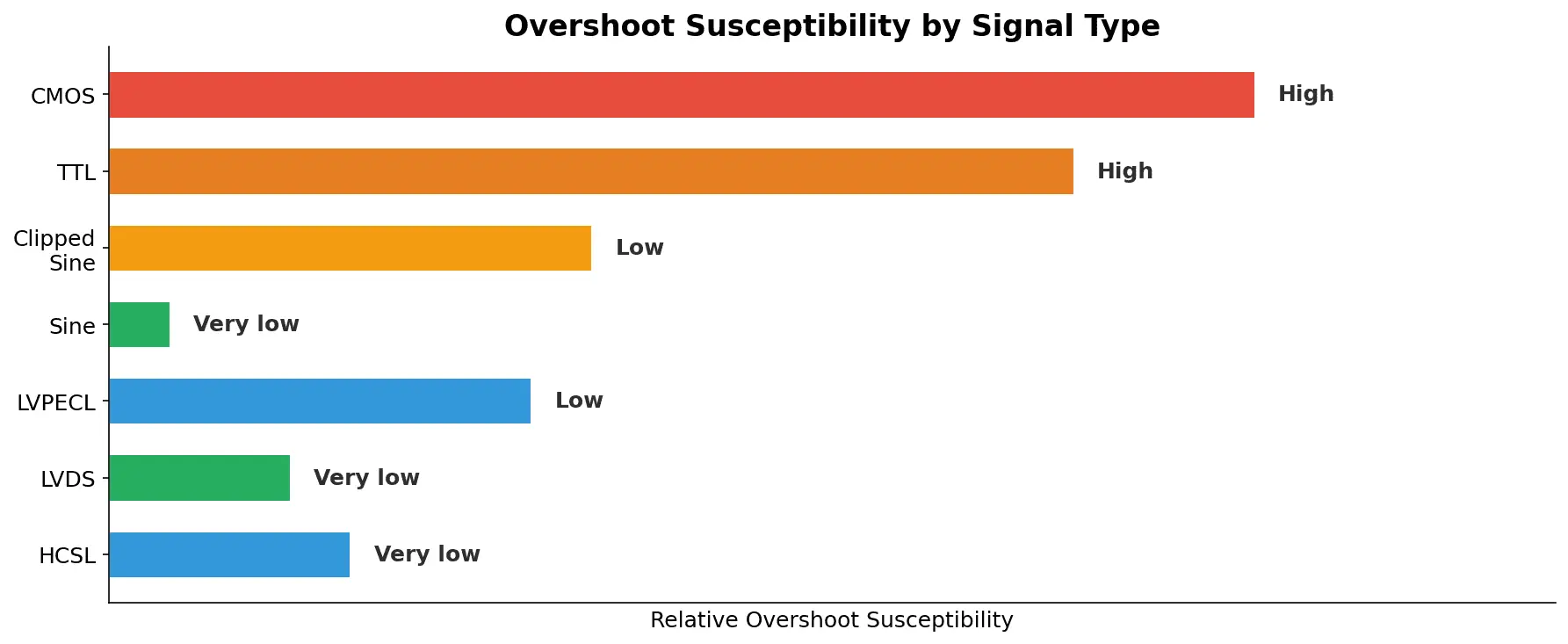

6.3 Comparison: Overshoot by Signal Type

The susceptibility to overshoot differs significantly between the various output types. The following graphic shows the relative susceptibility in comparison:

6.4 Overshoot in Single-Ended Signals

CMOS: Most affected. The symmetrical P-/N-channel MOSFET drivers generate very steep edges that, combined with trace inductances, cause pronounced overshoot. Especially with modern low-voltage CMOS oscillators (1.8 V), the overshoot can be significant relative to the supply voltage.

TTL: Also susceptible, though for slightly different reasons. The asymmetric totem-pole output stage generates a brief current spike on the rising edge when both transistors are simultaneously conducting (cross-conduction). The typically somewhat slower edges compared to modern CMOS slightly mitigate the problem.

Clipped Sine Wave: Significantly less susceptible. The limited amplitude peaks and relatively soft edges produce much less high-frequency energy that could excite reflections and ringing. The clipping acts as a natural amplitude limiter that suppresses overshoot already in the signal.

Sine wave: Virtually immune to classic overshoot. Since the signal contains no abrupt edge transitions, no broadband energy pulse is generated that could excite line resonances. However, impedance mismatches can lead to standing waves and reflections that alter the signal amplitude at certain points. This is controlled by classic RF termination (50Ω or 75Ω termination).

6.5 Overshoot in Differential Signals

LVPECL: Inherently well suppressed thanks to the current source output stage. The current steering naturally limits the maximum slew rate. With insufficient termination, reflections can still occur since LVPECL operates at very high frequencies. The correct Thevenin or emitter follower circuit is crucial here – not primarily because of overshoot, but to ensure the correct operating point and avoid reflections.

LVDS: Very robust by design. The current-driven driver delivers a constant current of typically 3.5 mA into the 100 Ω differential termination, physically limiting the voltage swing. Even with impedance discontinuities, reflections remain small since the low voltage swing of only 350 mV provides little energy for disturbances. LVDS is one of the most forgiving standards regarding signal integrity.

HCSL: Behaves similarly to LVDS due to its current-based architecture. The very low voltage swing and 50 Ω termination to ground ensure clean impedance matching. In the PCIe specification, the permissible overshoot is explicitly defined and tightly toleranced, so HCSL-compliant oscillators inherently meet these requirements.

6.6 Countermeasures for Overshoot Control

The most effective measure for single-ended signals (especially CMOS and TTL) is a series resistor directly at the oscillator output, typically in the range of 22 to 47 Ω. This resistor, together with the trace impedance, forms a voltage divider that dampens the edge and absorbs reflections. The optimal value results from the difference between trace impedance and output impedance of the driver.

Additionally, short impedance-controlled traces, minimization of vias on the clock line, a continuous ground plane under the signal line, and sufficient decoupling capacitors near the oscillator (typically 100 nF ceramic plus 10 µF) all help. Some CMOS oscillator manufacturers also offer models with controlled slew rate (Slew Rate Control) that mitigate the problem already in the driver.

For differential signals (LVPECL, LVDS, HCSL), the correct, specification-compliant termination is the most important measure. Additionally, the two lines of a differential pair should always be routed with equal length and tight coupling to minimize skew (propagation delay differences) and maintain common-mode rejection.

7. Decision Guide

The choice of the right output type essentially depends on four factors: the required clock frequency, the logic family of the receiver, the available power budget, and the signal integrity requirements.

Application | Recommendation |

| General digital technology, µC, FPGA I/O (up to ~200 MHz) | CMOS – Simplest and most cost-effective solution, rail-to-rail, widest availability, flexible supply voltage (1.8–5.0 V) |

| Legacy 5V systems, industrial controls | TTL – Directly compatible with older 5V logic families; increasingly replaced by CMOS with 5V supply |

| RF applications, transformer-based circuits | Clipped Sine Wave or Sine – Lower harmonic content reduces EMC problems and enables precise frequency synthesis |

| High-speed network equipment (>622 MHz) | LVPECL – Highest switching speed, ideal for SONET/SDH, Ethernet PHYs, and backplane clocks |

| FPGA clocking, serial data transmission, display interfaces | LVDS – Optimal compromise of speed, power consumption, and EMC behavior |

| PCI Express Reference Clock | HCSL – The only clock standard specified by PCI-SIG for PCIe systems |