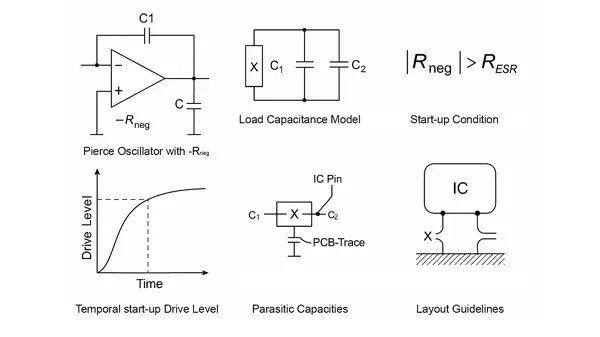

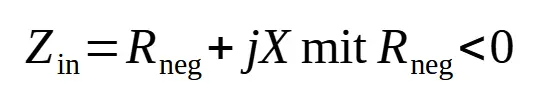

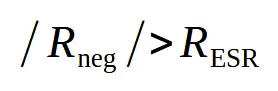

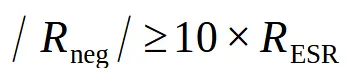

This means that the value of the negative input resistance must be greater than the series resistance (ESR) of the crystal.

Only then will there be a net amplification that leads to oscillation.

F.2: Influence on the transient response safety

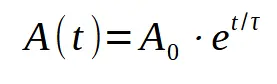

If the value of the negative input resistance is too small (i.e. -Rneg is too weak), the following happens:

- The quartz receives too little energy → slow oscillation or no oscillation at all

- Oscillation only starts at a higher supply voltage or temperature

- Start-up in low-power operating modes becomes unreliable

Typical cause:

Some modern MCUs have weak oscillator amplifiers for efficiency reasons, which means that -Rneg is smaller than in older IC generations. At the same time, many designs work with small load capacitances or long traces, which increases parasitic losses.

Q.3: Why are crystals with low ESR particularly important?

The ESR of the crystal defines its internal losses. A low ESR means

- lower losses

- lower necessary counter-amplification

- high transient stability even with weak oscillator stages

- shorter start-up time

- More stable oscillation over temperature

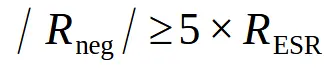

Practical recommendation:

- Use crystals whose ESR is significantly below the maximum value specified by the IC.

- If a microcontroller specifies a maximum ESR of 70 Ω, for example, a crystal with an ESR of 30-50 Ω is ideal. This leaves a sufficient safety margin against a possibly low negative input resistance of the oscillator.

F.4: Conclusion on the interaction of -Rneg and quartz ESR

The transient response reliability essentially depends on the following:

- the internal oscillator provides sufficient negative input resistance,

- the crystal has a sufficiently low ESR,

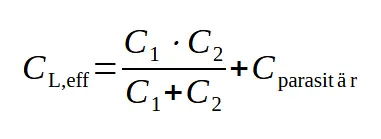

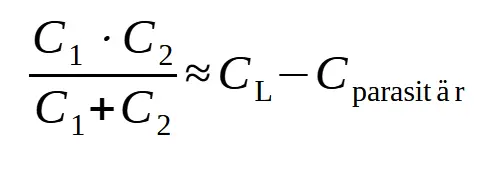

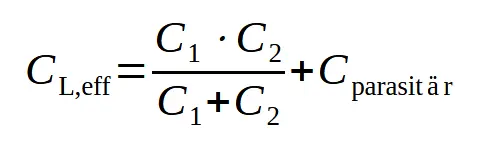

- the load capacitances are correctly dimensioned.

Only if the ratio of -Rneg to ESR is correct will the crystal start quickly, reliably and over the entire temperature and voltage range.